8 月 16 日,以“合·聚·创 共 IN 智能时代”为主题的“2023 英特尔(中国)学术大会”在南京开幕,邀请专家学者共话科技界前沿趋势,展示科研成果和技术解决方案。本次大会延续了英特尔“为智能而聚能”,推动中国产业界、学术界融合创新的不懈努力。

在大会开幕致辞中,南京市人民政府副市长吴炜表示:“南京是长三角特大城市、国家东部地区重要中心城市,科教资源丰富、产业基础雄厚、营商环境优良、发展前景广阔,英特尔公司一直以来与南京保持着良好的合作关系。本次举办的英特尔(中国)学术大会自 2003 年启动以来,已成为研究与展望技术发展趋势的重要窗口,和推动高等教育战略与产业化相结合的重要平台。”

英特尔公司高级副总裁、英特尔中国区董事长王锐也在视频致辞中表示:“从注重前沿探索的‘最初一公里’,到聚焦商业落地的‘最后一公里’,学术界、产业界在创新链条中密不可分。对英特尔来说,我们将更好地发挥在半导体技术、软硬件产品、可持续计算、开放生态等方面的优势,与大家一起为智能而加速。”

当天,英特尔还举办了“英特尔学术英才计划”颁奖典礼,共有 6 位来自国内高校和科研院所的青年才俊获得了英特尔提供的技术指导和奖金资助。接下来,“英特尔中国学术英才计划”将通过组织技术研讨会、学术沙龙、能力提升论坛等方式,搭建更大规模的产业界、学术界交流平台。此外,英特尔宣布全面推出“英特尔创新飞轮计划”,探索挖掘学术界种子项目,促进其产业化落地,推动产业界、学术界合作的进一步升级。

在主题演讲环节,英特尔研究院副总裁、英特尔中国研究院院长宋继强围绕“多维技术创新推进算力千倍提升”这一主题,介绍了英特尔如何通过制程、封装等半导体底层技术的持续创新,以及对神经拟态计算、集成光电和量子计算等未来计算领域的探索,推进高能效比下的指数级算力增长。同时,宋继强也分享了英特尔在助力高质量数字人才培养方面的长期实践。据介绍,英特尔中国从 1993 年就开始和学术界进行人才培养的合作,并从 2003 年开始举办了英特尔(中国)学术大会,英特尔希望在数字化转型的关键领域,和中国的学术界一起进一步探讨新产业化落地的机会。

英特尔半导体底层技术实现了哪些创新?

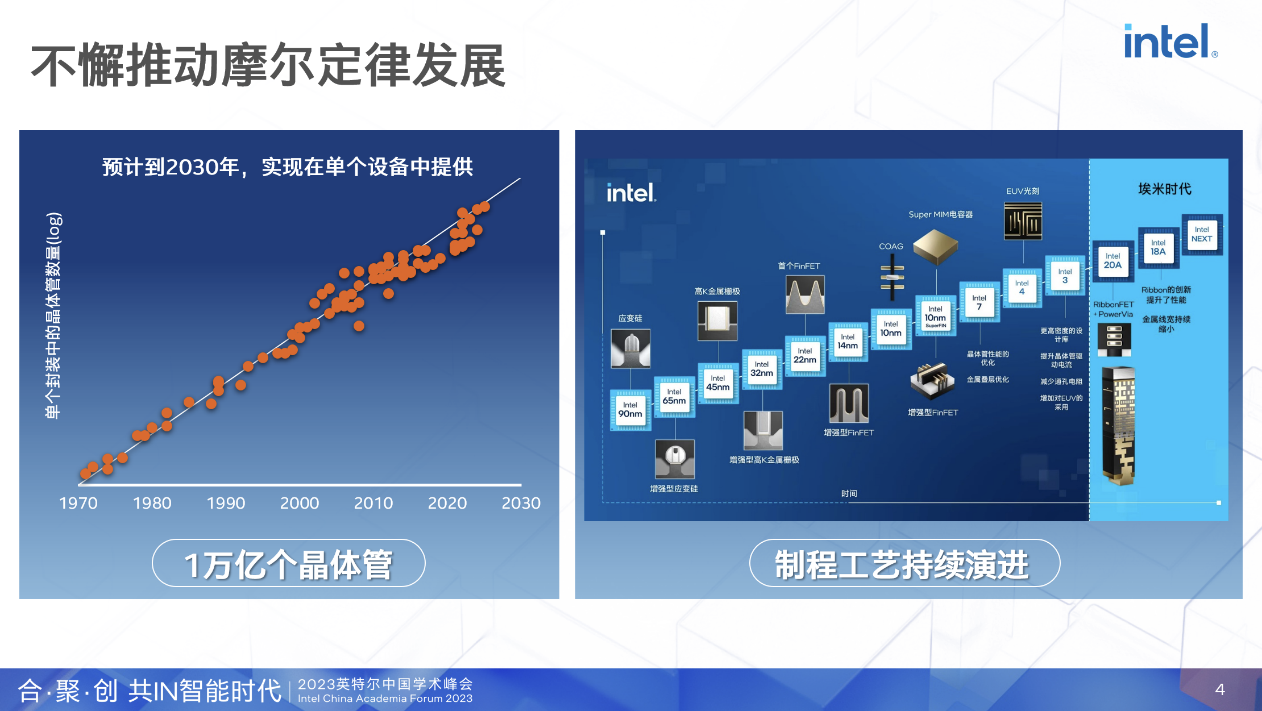

当前,英特尔在单一计算设备当中可集成 1000 多亿个晶体管,到 2030 年,英特尔计划在单一计算设备当中集成一万亿个晶体管。宋继强表示,要想实现这一目标,首先需要依靠半导体制程技术继续微缩晶体管,其次还要利用先进封装技术在单个封装内封装多个芯片。

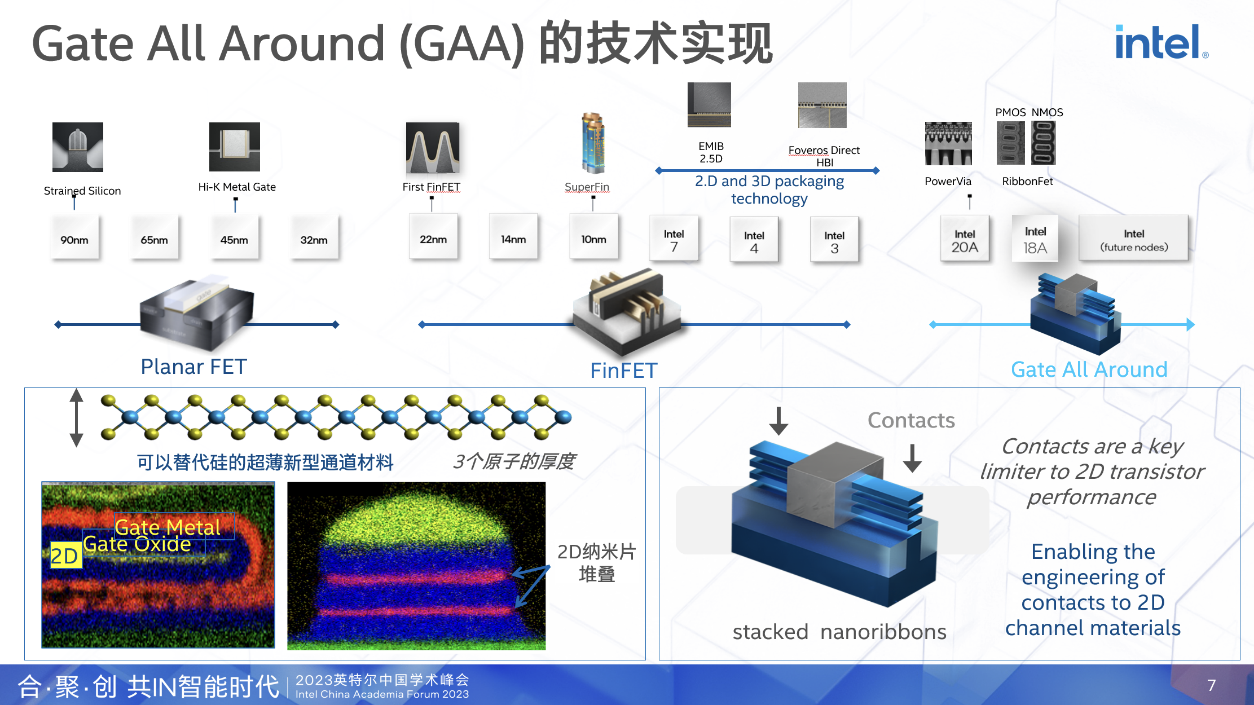

从半导体制程工艺的持续演进路线中可以看到,在 65 纳米的增强型应变硅、45 纳米的高 K 金属栅极和 22 纳米的首个 FinFET,英特尔通过技术创新引领行业突破了一些瓶颈。在 Intel 4 和 Intel 3,英特尔开始大规模引入 EUV 光刻技术,旨在在密度和半导体效能方面超越国际一流水平。接下来,即将迈入埃米时代(1 埃米相当于 0.1 纳米)。宋继强表示,从 Intel 20A 到 Intel 18A,在这个阶段,英特尔有信心回到制程的领先地位。

宋继强提到,在 Intel 7 阶段,英特尔在 EUV 的使用上较少,主要依赖 DUV 技术,因此在制程上遇到了不少困难,导致了一些延误。从 Intel 4 开始,英特尔逐步引入 EUV 技术,而 Intel 3 则完全采用 EUV 技术,在这两个节点上晶体管的结构并未发生变化,仍然是 FinFET 结构,然而 EUV 技术的广泛应用使得效能得到了显著提升。

而在 Intel 20A 和 Intel 18A 这两个关键性的节点,英特尔引入了两个革命性的技术:第一个是全环绕栅极晶体管 RibbonFET,这是一种全新的晶体管架构;第二个是背面供电技术 PowerVia。此外,在工具层面,高数值孔径的 EUV 对于提升制程工艺的良率也有重要意义。宋继强认为,综合这三个方面,英特尔有信心在 Intel 18A 这个阶段重夺制程领先性。

全环绕栅极晶体管 RibbonFET

随着晶体管微缩,晶体管结构从平面晶体管到 3D 晶体管,最后到达全环绕栅极晶体管成为了必然的选择。因为随着晶体管尺寸的缩小,通道尺寸也需缩小,栅极也需要缩小,这会带来接触面的变化,进而增加了控制的难度,本身栅极变小之后,短通道效应也会更加明显。所以,全环绕栅极晶体管的生产制造有很高的挑战。

在 Intel 20A 节点上,英特尔将能批量生产 RibbonFET,并实现出色的性能,也开始进行产品级别的生产。在此阶段,英特尔仍在使用硅制材料,此外,英特尔还在研究两项重要技术,一个是通过新的超薄材料,如过渡金属氟化物(它的厚度只有 3 个原子,是非常薄的 2D 材料),英特尔考虑将这种材料用于整个晶体管的通道,因为它在尺寸方面具有优势,它还能够克服硅材料在缩小后出现的短通道效应问题,这使得它成为未来 2D 纳米片堆叠中的首选材料之一。同时,当这种材料变得更小之后,英特尔需要优化金属杆的功率器件,以确保更好的通断控制。据悉,这两个技术正在同步进行研发,并将应用于后续的制程中。

背面供电技术 PowerVia

据介绍,背部供电也是一个非常大的技术创新。在以前的制程中,晶体管直接集成在硅基底上,上方有多层金属层,这些金属层既负责供电,又负责信号传输。在尺寸较大的情况下,这样的设计是可行的,然而随着尺寸的缩小,这种做法变得越来越具有资源竞争性,让后续的布线变得越发困难。在未来的应用需求中,特别是在 AI 广泛应用之后,算力强、体积小、功耗低、密度高对芯片而言将是至关重要的。为了满足这些需求,不光要有新的晶体管结构,在生产晶体管的时候,还要考虑供电的优化。

而背部供电技术把供电全部移到晶圆背面,让供电层和信号层完全分离,这种技术带来的好处是多方面的,它减少了复杂性,使供电和信号传输之间的干扰减少到最低,可以更好地满足高性能、低功耗的要求。

宋继强表示,RIbbonFET 和 PowerVia 这两项技术都会在 Intel 20A 和 Intel 18A 启用,在明年的产品当中就会开始应用。目前,英特尔使用一个内部工艺节点来解耦 PowerVia 和 RibbonFET 的开发与测试,将相关的功能模块进行划分,逐步引入、测试,以降低直接到达新节点所带来的风险。

在封装技术方面,通过 3D 先进封装 Foveros 技术,英特尔在垂直方向上集成多个芯片,不断缩小凸点间距,以进一步提升技术的性能。目前英特尔在产品路线图上已经在导入的,一个是 Foveros Omni 技术,它可以把凸点间距缩小到 25 微米,而 Foveros Direct 则通过混合键合技术(hybrid bonding)进一步把凸点间距缩小到 10 微米。此外,目前在实验室里研发的下一代混合键合技术,还可以进一步把它缩小到 3 微米,因此可以大幅度减少芯片封装时需要的尺寸。

未来计算领域探索:如何提升高能效算力与数据传输?

在演讲中,宋继强还分享了英特尔对神经拟态计算、集成光电和量子计算等未来计算领域的探索,推进高能效比下的指数级算力增长。

宋继强表示,在高能效计算方面,不能仅仅采用传统的标准计算思维,例如制造 AI 加速卡。随着技术不断发展,某些问题如视觉问题等,已经很难靠编程来解决,因此要借助数据驱动的方法,通过训练形成一个可以应用的大模型。这种方法涉及到密集的并行计算,即使在非工作状态时也会消耗能源,因此能效比相对较低。

未来,英特尔的目标是整合不同程度的人工智能能力。神经拟态计算是一种类脑计算芯片,它实际上通过模仿神经元的结构构建硬件,同时采用脉冲式神经网络这些新的技术,可以实现实时在线学习,也可以把多种不同的模态整合在一起。

英特尔在神经拟态计算方面做了很多尝试,并迭代了 Loihi 芯片。目前来看,和第一代相比,Loihi 2 在处理能力、带宽、连接多个方面实现了提升。这些提升一方面来自于架构设计的改造,同时也直接得益于制程的提升。Loihi 2 采用的是 Intel 4,而第一代是用的 14 纳米的制程。制程的提升直接导致英特尔在芯片能效上和密度上都有数倍的提升。

此外,英特尔还有一项最新的成果是 Kapoho Point 开发板,每个板把 8 个芯片直接叠起来互连,整个的计算密度非常大,能效比也非常高。目前,Kapoho Point 开发板在交通、金融以及通讯领域都有很好的应用前景。基于 Kapoho Point 开发板的英特尔神经拟态研究社区,有近 200 家创业公司、大企业和学校的参与。

在高能效数据传输方面,硅光技术是一个非常好的替代金属做服务器节点之间高带宽传输的技术,但在光和电的转换部分却无法做到非常有效的转换。宋继强表示,英特尔的目标是把它全部都能在一个封装好的芯片里面去完成,这是一个全集成的方案,它可以在能效上提高数倍,运行密度可以提高 100 倍,加上其它种种方面的改善,整体上可以达到千倍级别的提升。目前来看,英特尔已经可以通过 8 个波长去同步传输数据,能源效率已经实现了 4 倍的提升。而最终目标是要达到 16 个波长传输,能够达到 4Tbps/mm 的带宽密度。

2015 年,英特尔开始做量子计算芯片,目标是实现量子实用性,把它做成真正能在产业中使用的一套技术,而不只是学术研究。据介绍,此前英特尔发布了包含 12 个可控硅自旋量子比特的量子芯片 Tunnel Falls,它可以直接在英特尔的硅生产工艺上进行生产。

从整个的量子堆栈上来看,硬件层面既要有底下多量子比特的处理器,能够量产,又要有在超低温下能够对量子比特进行控制的技术,在室温情况下,主要是做电子器件。软件方面,从底下的量子点模拟器开始,一直做到上层的应用,中间的量子位控制模拟器是非常重要的,是在没有硬件的情况下完成很多实验的关键。

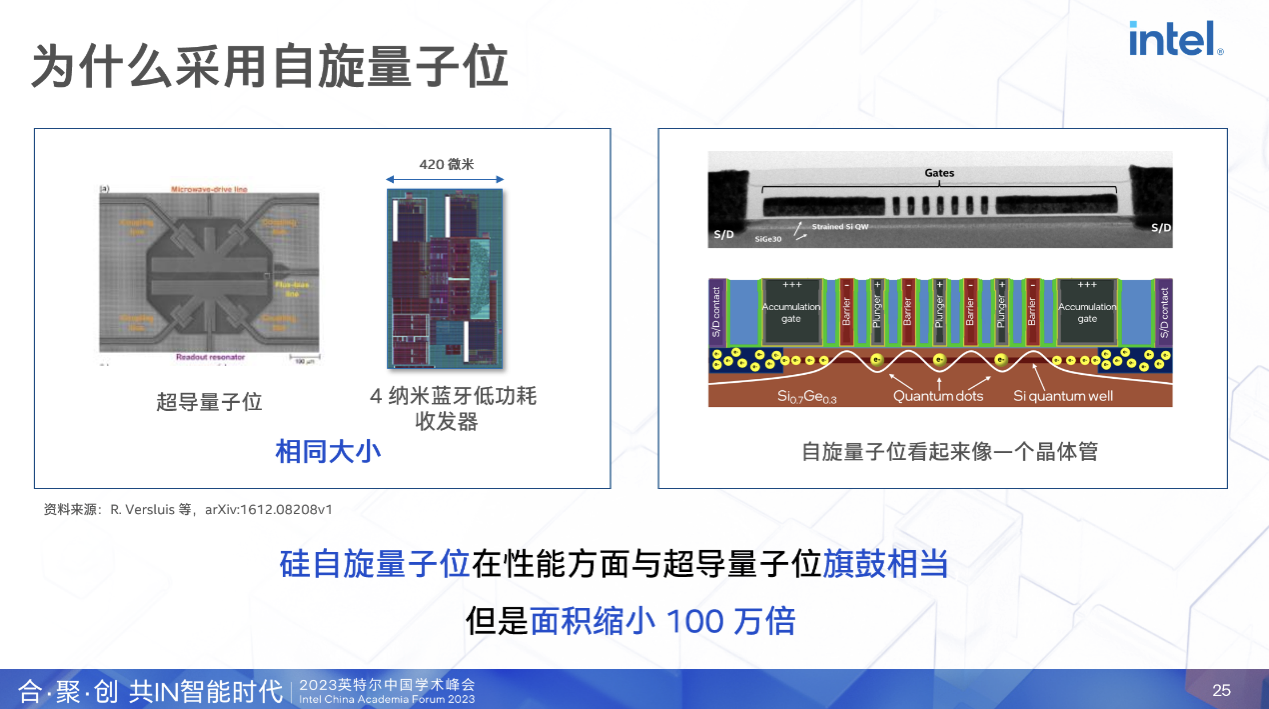

做超导量子位和自旋量子位是两条截然不同的路线。英特尔之所以选择硅自旋量子位,主要基于以下思考:当前超导量子位的体积依然很大,目前来看,一个量子位大小就跟一个 4 纳米的蓝牙低功耗收发器差不多,而硅自旋量子位在结构上和晶体管很相似,是可以在英特尔 300 毫米的硅晶圆制造工艺流程当中完全实现的,更易于推动产业化,面积上也缩小了 100 万倍。

评论