过去几年中,英特尔公司发起了很多有趣的项目,其中之一就是 XPU。XPU 的理念是使用多种计算架构充分满足单一负载的复杂计算需求。在实践中,英特尔不仅为此开发了 CPU 和 GPU 这样的通用计算芯片,还发展了 FPGA 和 VPU 等针对特定用途的硬件。在软件层面上,所有这些硬件都由英特尔的 oneAPI 软件栈统一调配。这一软件栈的设计目标是抽象出各种硬件的差异,方便开发人员跨多种计算架构开发应用。

英特尔一直表示他们的 XPU 计划才刚刚起步。在今年 2 月 17 日的英特尔年度投资者会议上,这家公司终于披露了 XPU 概念的下一步规划,即一个代号为 Falcon Shores 的新项目。

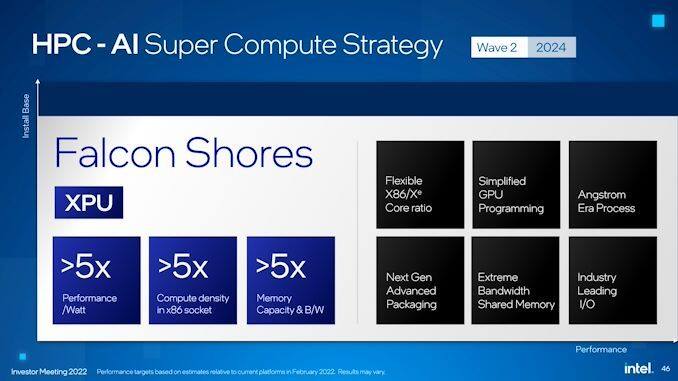

该项目主要针对超级计算/HPC 市场,其核心是一个新的处理器架构,可以将英特尔的 x86 CPU 和 Xe GPU 硬件置入同一颗 Xeon 芯片中。它计划在 2024 年发布,且英特尔预计它将提供 5 倍以上的每瓦性能和 5 倍于该公司当前平台的内存容量。

从非常高级的层面来看,Falcon Shores 看起来是一个用于服务器的 HPC 级 APU/SoC/XPU。虽然英特尔目前只提供了最基本的细节,但这家公司坦承,他们正在将 x86 CPU 和 Xe GPU 硬件合并到同一颗芯片中,并设法充分利用两者之间的协同作用。

而且,鉴于他们提到了先进的封装技术,可以肯定的是英特尔还有着比单片 die 更加复杂的设计方案,可能是独立的 CPU/GPU tile、HBM 内存(就像在代号 Sapphire Rapids 的 Xeon 芯片上使用的那样),或者是其他一些全新的设计。

再深入一点来讲,虽说整合多个独立组件往往会带来很多长期收益,但从这次发布来看英特尔的计划绝不只是将 CPU 和 GPU 整合到一颗芯片中(他们今天已经在消费级产品线这样做了)那么简单。

相比之下,英特尔高级副总裁兼加速计算系统和图形(AXG)集团总经理 Raja Koduri 的演讲清楚地表明,该公司希望赢得需要处理海量规模数据集的 HPC 用户的市场——那么大的数据集没法轻松放入独立 GPU 的内存里面。

相比之下,融合了 CPU 与 GPU 的芯片可以直接访问超大容量的 DDR 内存池,用不着花时间等待显存数据(相对)缓慢刷新,后者仍然是今天独立 GPU 的一大缺陷。

对于数据集规模超大的场景来说,即使有像 NVLink 和 AMD 的 Infinity Fabric 这样的高速接口,由于 HPC 级处理器操作数据的速度非常快,在 CPU 和 GPU 之间交换数据的延迟和带宽代价仍然相当高昂。因此如果能尽可能缩短这一链路的物理距离,就可以节约很多能源并提升性能。

同时,英特尔还骄傲地表示 Falcon Shores 可以灵活配置 x86 和 Xe 核心之间的比例。虽然这里隐藏了很多复杂的技术细节,但从高层次上看,这家公司正在考虑提供具有不同数量计算内核的多个 SKU — 每种 SKU 都可能有着数量各异的 x86 CPU 和 Xe GPU tile。

从硬件的角度来看,英特尔似乎计划将其下一代技术中的大部分都投入到 Falcon Shores 中,以满足超算市场的需求。这款芯片预计将基于“埃米时代工艺”制造,考虑到 2024 年的发布日期,该芯片可能会使用英特尔的 20A 工艺。除了未来的 x86/Xe 内核,Falcon Shores 芯片还将配备英特尔的“极限带宽共享内存”。

在所有这些技术的支持下,英特尔预计 Falcon Shores 将在几个指标上比他们现有的一代产品提升 5 倍左右,具体来说是每瓦性能提高 5 倍、单个(Xeon)插座的计算密度提高 5 倍、内存容量提高 5 倍,以及内存带宽提高 5 倍。简而言之,该公司对 Falcon Shores 的性能有很高的期望,考虑到它所针对的是竞争激烈的 HPC 市场,这也是很合理的。

也许最有趣的是,为了获得这样的性能提升,英特尔并不只是从原始的硬件吞吐量方面来考虑问题。Falcon Shores 的公告还提到,开发人员将可以使用针对该芯片设计的“大大简化的 GPU 编程模型”,这表明英特尔所做的工作不只是把一些 Xe 内核装进芯片而已。这一举措的效果还有待观察,但简化 GPU 编程一直都是 GPU 计算行业的一个主要目标,特别是对于融合 CPU 和 GPU 核心的异构处理器来说更是如此。如果这些高吞吐量的芯片更容易编程,也就更容易被开发人员所接受,而且减少/消除同步和数据准备的要求也可以在很大程度上帮助开发人员。

随着该公司继续推进该项目的研发工作,未来几年内我们应该能听到更多关于 Falcon Shores 的消息。

原文链接: